波多野结衣qvod Chiplet邻接,有了“光”有筹谋

2019 年,CEA-Leti 成为首个获取手用 3D 架构将芯片集成到有源中介层上的组织。Leti 过甚互助机构 CEA-List 的酌量东谈主员面前正在在此基础上开发有源光学中介层,以最小的延伸邻接大齐芯片。跟着行业在越来越大的晶圆上坐褥越来越多的芯片波多野结衣qvod,这项责任的策画是复杂的系统级封装。

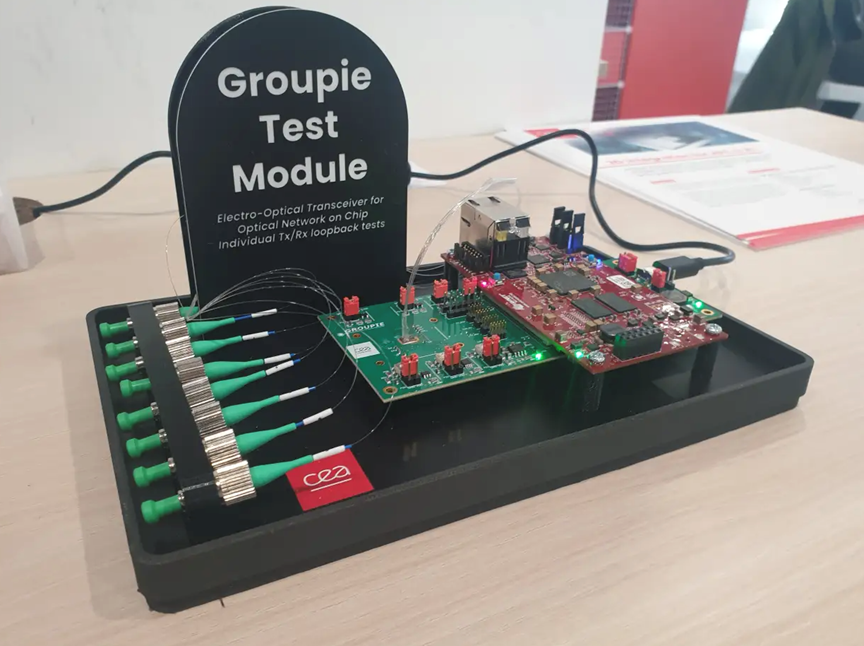

本年夏天,在法国格勒诺布尔举行的 Leti 翻新日 2024 看成上,CEA 酌量东谈主员共享了最近开发的 Starac,这是一款基于芯片的光学片上收集 (ONoC) 演示器,它开发在有源光学中介层上,模仿了 Leti 在电子中介层方面的早期成立。CEA-List 高档酌量员 Yvain Thonnart 示意:“咱们保留了在芯片之间路由信息的才智,而无需在大齐中间芯片之间最初。通过使用光子学,咱们筹谋将延伸大大缩短,这比咱们之前的责任和现在行业所作念的要好。”

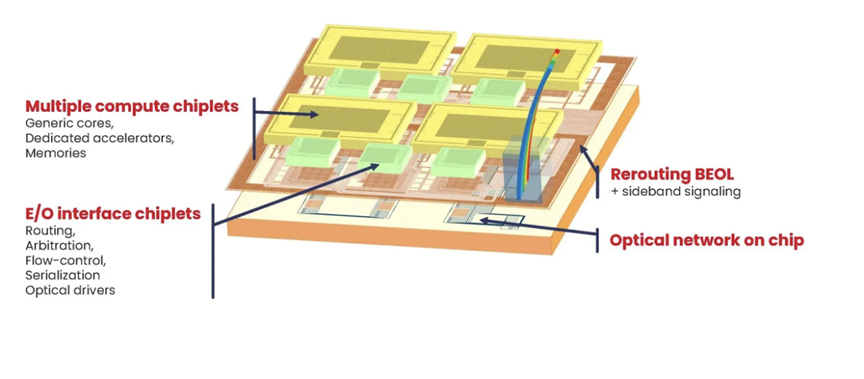

天然无源中介层提供结构复旧和相邻芯片之间的邻接,但有源中介层集成了更复杂的电路,不错添加逻辑,在远距离芯片之间路由数据,而无需全部进行最初。无源中介层需要通过最初传输数据,这会加多延伸和功耗。跟着光学互连的日益普及,翌日的游戏规章窜改者将是使用光子学而非电子学的有源中介层,以进一步缩短功耗和延伸。

描写 CEA-Leti 的 ONoC 拓扑的浮浅设施是将其称为环,但仔细不雅察系统中的每个波导就会发现它们以复杂的螺旋状轮回。因此,每个芯片齐不错与任何其他芯片进行通讯,而无需跳过一系列中间芯片。“这有点像大型收集合的点对点,因为咱们的架构中莫得效于通讯的连合舍弃器,”Thonnart 说。

“在大型谋略系统中,有多个带有中枢的谋略芯片和多个 HBM [高带宽内存],播色网”他说。“英特尔、AMD 和 Nvidia 的最新处理器齐是如斯。从中枢转到隔邻的 HBM 很容易。但若是您需要从中枢转到更远的 HBM,那么您需要践诺一系列操作才能获取数据。使用咱们的惩办有筹谋,延伸将大大改善,因为与更传统的架构中需要经过扫数最初的旅程比拟,在咱们的片上光学收集合指令的光的固有延伸终点小。”

CEA-Leti 的光学中介层本领名为 Starac,该酌量机构在本年夏天举行的 Leti 翻新日 2024 上展示了该本领(如上图)。Starac使用硅光子学代替铜来传输数据,从而自动晋升性能并缩短延伸和功耗。它还支捏无法使用传统设施构建的路由。与用于邻接芯片的传统无源中介层不同,有源光学中介层集成了逻辑电路,可兑现平直通讯,而传统无源中介层需要多个才智(或最初)才能使数据在远距离芯片之间传输。

CEA-Leti 推出的Starac演示器展示了这项本领,其片上收集 (ONoC) 想象由四个芯片组(每个芯片组有 16 个内核)、六个电光驱动器、Ø10 x 100 μm 中间工艺 TSV 和四个前端布线层构成。其螺旋波导结构(无法在无源中介层上构建)使芯片组粗略平直互相同讯,无需中间最初。这排斥了传统多芯片组想象中常见的延伸,跟着芯片组数目的贬抑加多,延伸变得越来越遑急。

关于面前和翌日的多芯片系统级封装而言,减少延伸、加多带宽并舍弃功耗至关遑急。Starac 系统中的光学中介层允许多个处理器和高带宽内存单位快速高效地交换数据,即使在系统内的长距离内亦然如斯。CEA-Leti 的责任记号着向使用光子学为 SiP 提供更快、更具可彭胀性的通讯惩办有筹谋迈出了遑急一步。

幽闲永不幽闲的新愚弄需求

新架构惩办的主要问题是,新愚弄需要数目大幅加多、功能越来越矍铄的处理器。跟着处理器数目的加多,需要更多的并行性,这意味着需要的数据不单存在于一个点。系统内的多个不同组件需要使用和重用交流的数据。不仅单个封装中的处理器之间需要快速数据传输,何况从系统外部到系统里面以及反之亦然。CEA-Leti 示意,其想象的本领不仅不错在单个封装上脱手,还不错彭胀以支捏两个或多个封装之间的传输。

Thonnart 示意:“咱们但愿通过这套光学套件兑现的策画,是让东谈主们拼装大齐芯片,而无用惦念物理集成。咱们在芯片间通讯圭臬化责任方面仍后起之秀,因为圭臬仍然侧重于两个芯片之间的点对点邻接。最终,咱们但愿匡助补充圭臬,使芯片粗略与专用的电光芯片对接,从而处理咱们片上光学收集的扫数方面。”

迈向工业化

与此同期,CEA-Leti 研发景色弘扬东谈主 Jean Charbonnier 示意,Leti 但愿通过 Starac 演示器展示该本领,从而勾引工业互助伙伴。Charbonnier 示意:“咱们但愿让使用新架构的系统想象师和代工场齐参与进来,让他们与咱们互助,为工业坐褥作念好准备。”

楠里 足交工业化谈路上的一项挑战是开发高效的制造工艺,以集成扫数中介层组件。“咱们还是为咱们的 Starac 演示器开发了许多新的工艺才智,”Charbonnier 说谈。“3D 互连处理方面的工程责任量宏大,因为它十足是新事物,需要多种不同的专科常识。”

必须礼聘 CEA-Leti 光电子和硅元件部门的群众来匡助惩办光子节点和芯片 3D 集成中固有的一些兼容性问题。举例,团队必须细目禁入区,以便他们粗略在不窜改信号的情况下使用硅通孔和波导。在开发竣工的演示器之前,必须单独进行酌量以考证不同的子进程。

现在演示景色还是完成,“咱们有许多事情不错改造,致使十足重作念,”Charbonnier 说。“举例,咱们不错将激光器平直放在开发上,以幸免光纤与激光器发生共振。而在封装方面,仍有很大改造空间。

“咱们但愿在翌日一年傍边开刊行业互助伙伴相干波多野结衣qvod,以匡助咱们惩办一些进程和封装问题,并让咱们更接近这项本领可能惩办的实质问题,”Charbonnier 补充谈。